计算机组成

目录

:link: https://www.coursera.org/learn/jisuanji-zucheng/home/info :desc: 北京大学 陆俊林

1. DONE 计算机组成章节介绍

2. DONE 计算机基本结构

- 推荐的主要教材是《计算机组成与设计》(英文版·第4版)Computer Organization and Design, Fourth Edition,作者:David A. Patterson John L. Hennessy;另外也推荐阅读 《Intel微处理器》(第8版)The Intel Microprocessors, Eighth Edition,作者:Barry B. Brey

2.1. DONE 101 电子计算机的兴起

2.1.1. ENIAC

- 为了火炮射击表而生

- 1946.2.14 完成

- 第一台 通用 计算机

2.1.2. ABC

- 1939 完成

- ENIAC 借鉴了它

2.1.3. EDVAC

- 《关于EDVAC的报告草案》

- 全称 “离散变量自动电子计算机”

- 1945

- 描述了 冯诺依曼结构

- 提出了储存器的概念

2.1.4. EDSAC

- 1949.5.6. 正式运行

- 第一台实用的存储式计算机

- 第一台采用冯诺依曼结构

2.1.5. UNIVAC

- 开启了商用计算机时代

2.2. DONE 冯诺依曼结构的要点

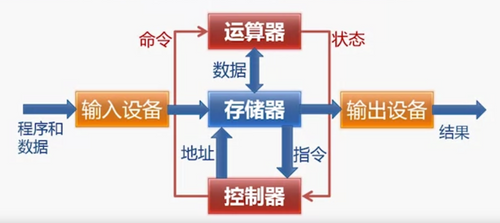

- 计算机由5部分组成

- 储存器 M

- 控制器 CC Central Control

- 运算器 CA Central Arithmetic

- 输入设备 I

- 输出设备 O

- 程序 与 数据 以 二进制 的存放在存储器中,存放位置由储存器的地址指定

- 计算机在工作时 自动 从存储器中 取出指令 加以执行

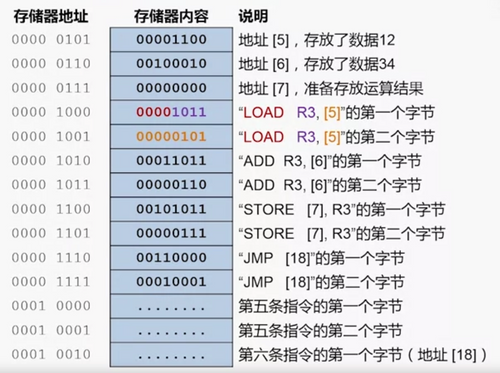

- 主存的组织形式

- 地址: 每个存储单元的序号

- 内容: 存储单元存放的信息

因为计算机运行非常迅速,程序储存在存储器中,控制器就不需要等待用户下发的指令,这样子能节省大量的时间

2.3. DONE 冯诺依曼结构的小故事

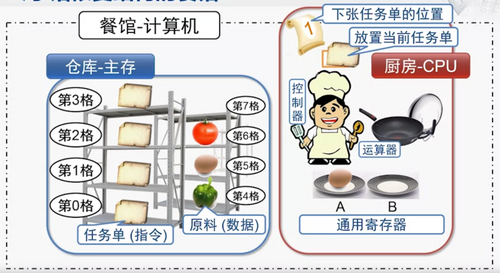

2.3.1. 计算机执行指令的过程

- 取指

- 译码

- 执行

- 回写: 保存结果

2.4. DONE 计算机结构的简化模型

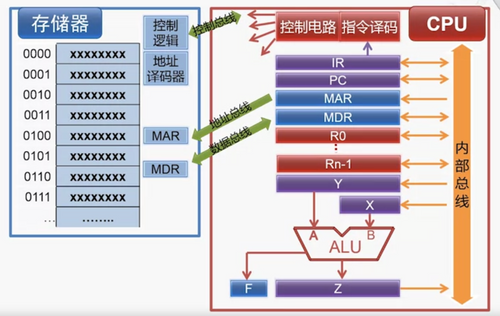

2.4.1. 存储器

- 如果 存储单元 按 字节 编址, 那么一个存储单元可以存放 8 位

- 存储单元的地址是唯一的

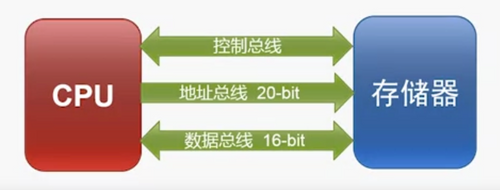

- 与CPU通过 系统总线 (system bus) 相连

- 控制总线

- 控制逻辑: 接受CPU的读、写、完成等控制信号

- 地址总线: 传输存储单元地址。宽度为 n , 表示CPU最多可以管理 2n 个存储单元。 比如 32位 系统只能管理4G内存

假设控制器有10条地址总线,其对应的储存空间就为 210, 1KB

- MAR (Memory Address Register) 存储器地址寄存器。 用来存放CPU正在读写的存储单元的地址

- 数据总线: 一般为存储单元的整数倍。

- MDR (Memory Data Register)。 用于存在CPU正在读写的存储单元的数据

2.4.2. 控制器

- 完成 取指、分析、执行等功能

- IR (指令寄存器): 存放正在执行或即将执行的 指令

- PC (程序计数器): 储存下次执行的指令的 地址

- MAR: CPU 的地址寄存器。 流动方向是 单向 的

- MDR: CPU 的数据寄存器

- 指令译码部件: 对 IR 存放的指令进行译码, 确定存放的是哪条指令

- 控制电路: 确定好指令后, 产生控制信号。 在时序脉动的同步下控制各个部件的动作

2.4.3. 运算器

- 完成 + - * / 算术运算 和 ! & | 逻辑运算

- ALU (算术逻辑单元)

- ALU 对 X, Y 中的数据进行运算, 将结果保存到 Z 。

- F 则用来存放运算结果的状态 (零/正负/进位/溢出)

- R0 … Rn 通用寄存器, 用与临时存放数据。 数据可能来源与存储器, 其他通用寄存器, ALU的输出

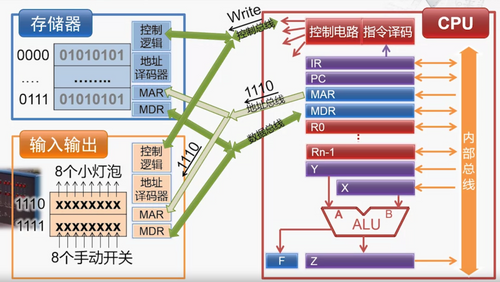

2.5. DONE 计算机执行指令的过程

- 执行指令: ADD R0,[6] — 将 R0 与 地址为 6 (0110) 储存单元 的数据相加, 将结果保存到 R0

- 初始状态:

- PC: 0001 ,该指令地址

- [0001]: 指令内容

- R0: 0011

- [6]: 0010

- 过程:

- 取指

- 控制器: 将 PC 的地址 送往 存储器。 PC[0001] -> 内部总线 -> MAR[0001] -> 地址总线

- 控制电路 -> 控制总线[Read] -> 控制逻辑

- 存储器: 地址总线 -> MAR -> 地址译码器 -> [0001] -> MDR -> 数据总线

- 控制逻辑 -> 控制总线[Ready] -> 控制电路

- 控制器: 数据总线 -> MDR -> 内部总线 -> IR

- 控制器: PC 地址+1

- 分析

- IR -> 指令译码器 -> 控制电路

- 执行

- 控制器: 控制电路 -> MAR [0110] -> 地址总线

- 控制电路 -> 控制总线[Read] -> 控制逻辑

- 存储器: 地址总线 -> MAR -> 地址译码器 -> [0110] -> MDR -> 数据总线

- 控制逻辑 -> 控制总线[Ready] -> 控制电路

- 控制器: R0 -> 内部总线 -> X, 数据总线 -> MDR -> 内部总线 -> Y

- 运算器: X,Y -> ALU -> Z,F

- 回写

- Z -> 内部总线 -> R0

- 取指

- 问题:

- 送往 是什么操作的?

- 数据是如何传输的?

2.6. DONE 计算机输入和输出

- 外部记录介质 R : 例如 穿孔纸带, 硬盘

- 输入

- 控制电路 -> 控制总线[Read] -> 控制逻辑

- MAR[控制器] -> 地址总线 -> MAR[输入设备] -> 地址译码器

- MDR[输入设备] -> 数据总线 -> MDR[控制器]

- 输出

- 控制电路 -> 控制总线[Write] -> 控制逻辑

- MAR[控制器] -> 地址总线 -> MAR[输出设备] -> 地址译码器

- MDR[控制器] -> 数据总线 -> MDR[输出设备]

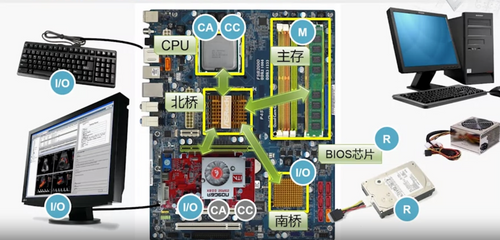

2.7. DONE 冯诺依曼结构和具体实现

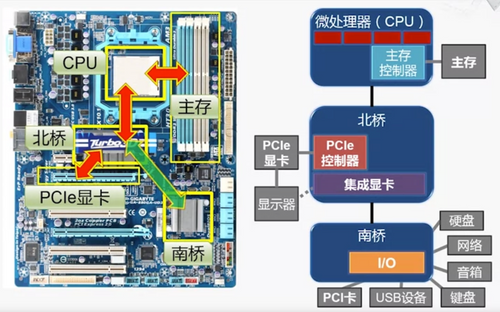

- CPU 与内存通过 北桥 相连

- 南桥 与各种 I/O 相连

- BIOS 芯片(属于 ROM)与 南桥 北桥 相连。 CPU初始指令从 BIOS 获得

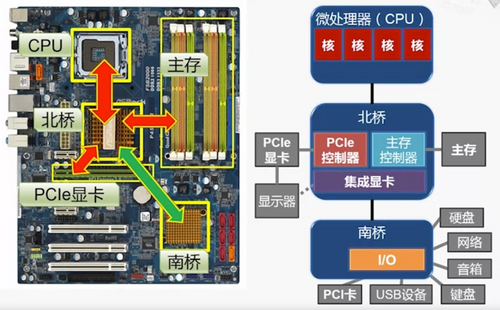

2.7.1. 南北桥架构演变

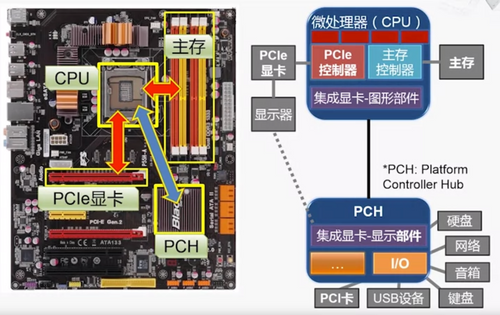

- 北桥负责 CPU 与 主存间的数据传输

- CPU 直接与主存相连, 大大提交两者间的数据传输

- PCIe 控制器也移到CPU, CPU与显卡直接相连,提升传输效率

- 北桥剩余的功能移动到南桥

- 南桥改名为 PCH

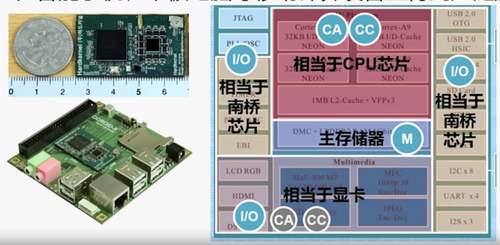

- 系统芯片 (System-on-a-Chip SoC)

- 将上述集成为单一电路的集成电路

摩尔定律: 每隔18个月,集成电路上的晶体管数目会翻一倍

3. DONE 指令系统体系结构

3.1. DONE 设计自己的计算机

3.1.1. 指令分类

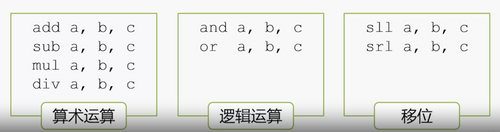

- 运算类

- ADD R,M

- 传送类

- LOAD R,M 读

- STORE M,R 写

- 转向类

- JMP L 下条指令地址转向到 L(存储单元地址) 去获取

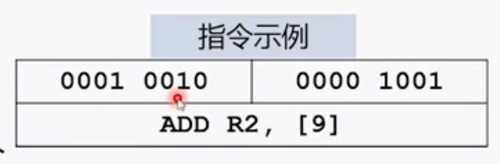

3.1.2. 指令示例

- 一条指令2个字节

- 第一个字节 高位(前4bit) 为 操作码 , 低位(后4bit) 为寄存器号

- 可以有 24 16 个操作码 (ADD LOAD 等)

- 可以有 24 16 个寄存器 R0 … R15

- 第二个字节为存储器地址

- 可使用 28 256 个字节的存储器

3.1.3. 任务示例

将 M1 与 M2 的内容相加, 然后存入 M3, 最后转向 L

- 设 M1=5, M2=6, M3=7, L=18

- 汇编程序则为

- LOAD R3,[5]

- ADD R3,[6]

- STORE [7],R3

- JMP [18]

- 存储器片段为:

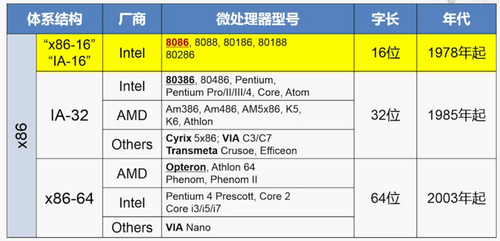

3.2. DONE x86 体系结构

3.2.1. x86 体系结构 常见型号

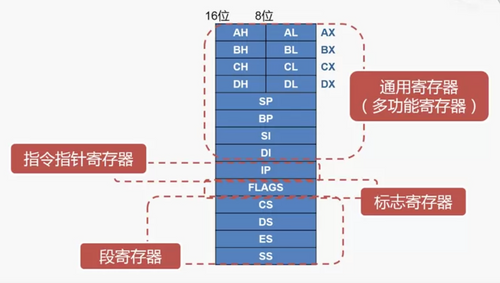

3.2.2. 8086 处理器

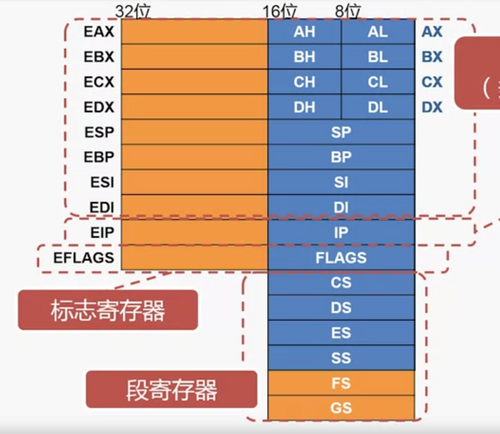

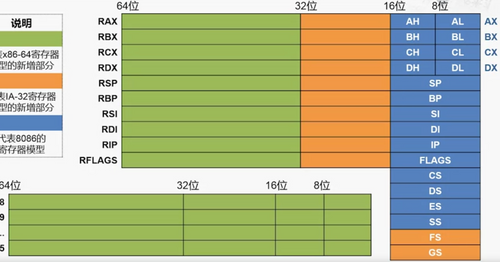

- 内部的通用寄存器为 16 位, 可处理 16 位和8位的数据

- 地址总线 20 位, 可寻址 220 (1MB) 的数据

- 数据总线 16 位

4个数据寄存器

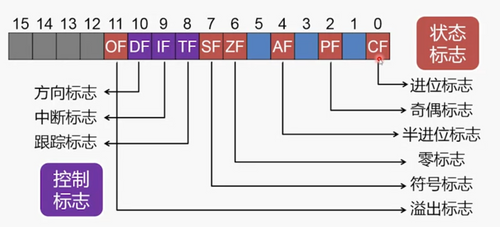

- 一个标志寄存器

- IP 是作为 PC 来使用

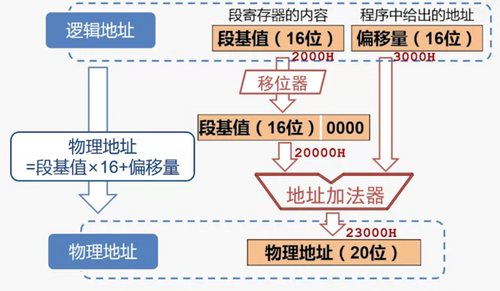

- IP 的寻址能力位 216 (64K), 而地址总线为 220

IP 与 段寄存器联合从而获得 220 的寻址能力

逻辑地址与物理地址的转化

3.2.3. 80386 处理器

第一款 x86 系列的 32 位处理器

- 各个寄存器扩展为 32 位

3.2.4. x86-64 的寄存器模型

与32位兼容

- 额外增加了8个通用寄存器(共16个)

3.3. DONE x86 指令简介

3.3.1. 指令分类

- 运算类: 加 减 与 非 等

- 传送类: 从存储器到通用寄存器 从通用寄存器到 I/O 等

- 控制类: 暂停处理器 清除标记位 等

- 转移类: 无条件转移 条件转移 过程调用 等

3.3.2. 程序示例

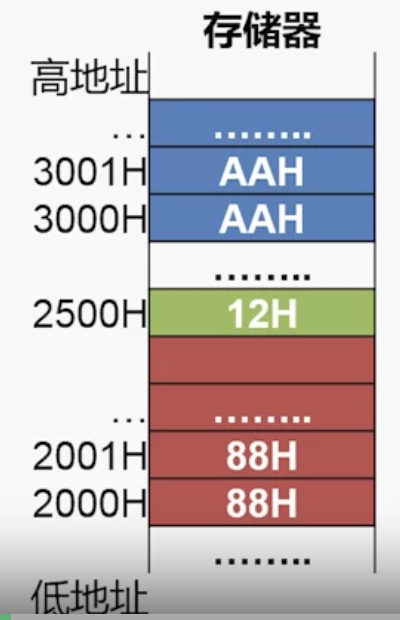

计算 [2000H] 和 [3000H] 起始的两个数之和, 数的长度存储在 [2500H]

- x86 传送类指令

- x86 运算类指令

- x86 转移类指令

- x86 控制类指令

- 汇编示例

- MOV CL,[2500H] 将 [2500H] 传送到 CL 寄存器

- MOV SI,2000H 将 SI 寄存器设置成 2000H 这个立即数

- MOV DI,3000H

- CLC 清除标记位 CF

- LOOP1: MOV AX,[SI] 将 SI 存储的地址指向的数据放入 AX; [2000H] 的数据存到 AX

- ADC AX,[DI] 将 DI 存储的地址指向的数据 与 AX 存储的数据 相加; [2000H] 与 [3000H] 的数据相加

- MOV [SI],AX 将 AX 存储的数据 存放到 SI 储存的地址指向的内存地址; 相加的结果写入 [2000H]

- INC SI 获取高位数的地址

- INC SI

- INC DI

- INC DI

- DEC CL 将数据长度减1, 当减到0时, 说明取够了的数据长度。 这时会把 ZF 置为 1

- JNZ LOOP1 检查 标志寄存器 的 ZF 标记位

- MOV AX,0H

- ADC AX,0H 会把进位结果写到 AX 中

- MOV [SI],AX 将前述的运算结果的最后一个进位结果写入存储器

为什么要 INC 两次?

— 从图中看出, 字长为2 ([2000H] 储存的是 AAH )

两次 INC 能够用 ADD SI,2

— 不能, ADD 会改变 CF

3.4. DONE 复杂的 x86 指令举例

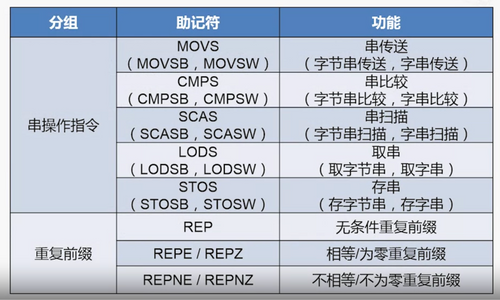

3.4.1. 串操作指令

- 对存储器中的数据串进行每次一个元素的操作

- 串的基本单位是 字节 或 字 (即一个元素)

- 串长度可达 64KB

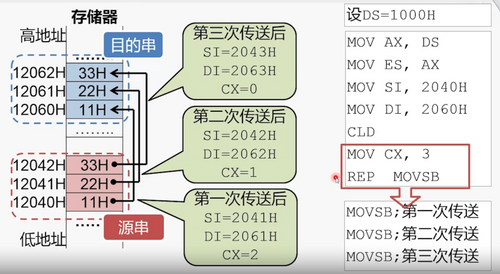

3.4.2. MOVSB

- 格式: MOVSB

- 操作: 在存储器中将特定位置的一个字节单元传送到另一个指定位置

- 没有显示的操作数

- 隐含的操作数: 源串地址 (DS:SI), 目标串地址 (ES:DI), 串的长度存储在 (CX)

- 硬件自动完成的操作:

- 处理完一个串元素操作后, 将 SI和DI 指向下一个串元素

- 如果有重复前缀, 则 CX <- CX-1

3.4.3. REP

- 格式: REP 串操作指令

- 操作: 当 CX != 0 时, 重复执行 串操作指令

3.4.4. 指令示例

- 传送: 将数据从存储器读到CPU, 然后再写入目标存储器位置

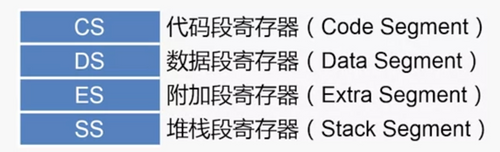

- DS, ES 是段寄存器, 段寄存器间不能进行相互写入,故用 AX 中转

- 标识寄存器 DF 位:

- DF=0 从源串 低地址 开始传送, 传送后 SI DI 自动增量

- DF=1 从 高地址 开始, 传送后 SI DI 自动减量

- 为了解决 源串和目标串有重叠的情况

3.5. DONE MIPS 体系结构

3.5.1. MIPS 的设计指导思想

- 全称: Microprocessor without Interlocked Pipeline Stages (无内部互锁流水线级的微处理器)

- 减少指令的类型

- 降低指令复杂度

3.5.2. 做法

- 固定的指令长度: 32 位 (一个字)

- 简化了从存储器取指

- 简单的寻址模式

- 简化了从存储器取操作数

- 指令数量少, 指令功能简单 (一条指令只完成一个操作)

- 简化指令的执行过程

- 只有 Load 和 Store 可以访问存储器

- 例如, 不支持 x86 的 ADD AX [0001H] 这种

3.5.3. 指令示例

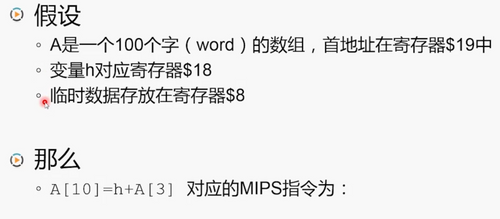

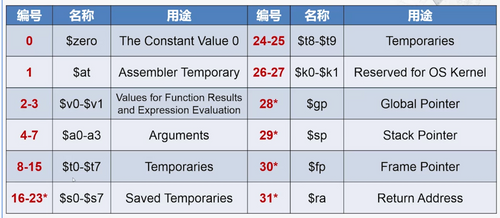

3.5.4. MIPS 寄存器

- 都是32位

- 可以使用编号或名称

3.6. DONE MIPS 指令简介

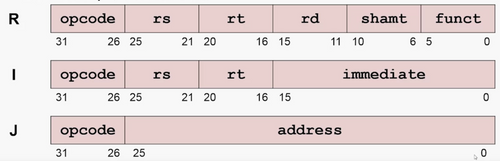

3.6.1. 基本格式

- R (Register) 型: 寄存器

- I (Immediate) 型: 立即数

- J (Jump) 型: 无条件转移

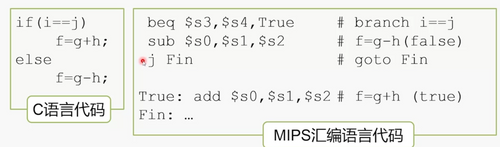

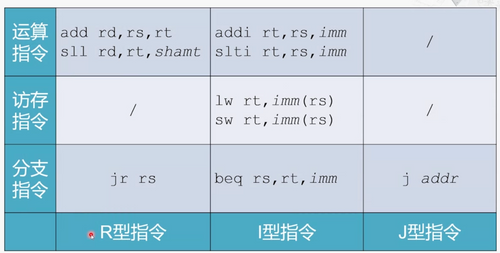

3.6.2. 分类

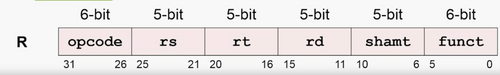

3.6.3. R 型

- opcode 指令类型, 都为 0

- funct: 和 opcode 组成操作码

- rs rt rd: 25 32 个寄存器 , rs rt 指定源操作数寄存器, rd 指定保存运算结果的寄存器

- shamt

- 用于指定移位指令的位数

- 对于非移位指令, 该域为0

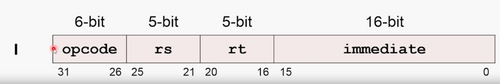

3.6.4. I 型

- opcode 指定指令操作类型

- rs 指定源操作数, rt 指定 保存结果

- immediate 操作的立即数 -216 ~ 216-1

- 对于访存指令, lw rt,imm(rs) 可以满足访存地址偏移量的需求

- 对于运算指令, addi rt,rs,imm 可能过小

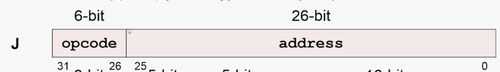

3.6.5. J 型

- 不需要判断条件

- 地址位移量为 -225 ~ 225-1

- 表达的地址位置范围 -227 ~ 227-1 (128MB), 视频是 \(\pm 2^{28}\) ?

- 到达更远的目标地址

- 多次调用 j

- 使用 jr rs (将地址存在寄存器)